ESP-DAP(1) 概述与定义

1 JTAG

JTAG(Joint Test Action Group) 是 1985 年全球主要电子器件制造商联合成立的行动小组,该小组于 1990 年公布了 IEEE 标准(IEEE 1149.1-1990: IEEE 标准测试访问端口和边界扫描架构)。这是一种用于在 PCB 上进行测试的 IC 级别实现标准接口。

并在 1994 年,加入了补充文档对边界扫描描述语言(BSDL)进行了说明。自此,该标准被全球的电子行业广泛采用。而后, JTAG 几乎成为了边界扫描的同义词。

接口名称: Test Access Port, TAP

1.2 电气特性

根据 JTAG 规范的不同版本,所需引脚数也是不同的。但无论哪个版本,只要一个 jtag 端口即可访问所有连接芯片。

1.2.1 IEEE 1149.1

这是 4,5 引脚的版本,允许多枚芯片通过菊花链连接在一起。

- TDI (Test Data In)

- TDO (Test Data Out)

- TCK (Test Clock)

- TMS (Test Mode Select)

- TRST (Test Reset) optional

1.2.2 IEEE 1149.7

这是 2 引脚版本,需要多枚芯片应星形连接。

- TMSC (Test Serial Data)

- TCK (Test Clock)

还有其他的双线版本存在,如 Serial Wire Debug (SWD) 和 Spy-Bi-Wire (SBW) 。

2 SWD

SWD(Serial Wire Debug) 是 JTAG 协议的变种,在电气连接上仅有两个必须的引脚。

SWD 使用 ARM CPU 标准双向有线协议,该协议在 ARM 调试接口 v5 中定义。这使得调试器能够成为另一个AMBA总线主机,用于访问系统内存和外设或调试寄存器。在 50 MHz时数据速率高达 4 MB/s。

- TMS -> SWDIO

SWDIO(Serial Wire Data I/O) 是双向信号。当没有连接调试单元时,SWCLK信号必须在目标上拉高。 - TCK -> SWCLK

SWCLK(Serial Wire Clock) 是单向信号。当没有连接调试单元时,SWCLK信号必须在目标上拉低。 - SWO (可选)

SWO(Serial Wire Output) 是来自目标的输出信号,通常与 SWD 信号一起使用以提供低带宽跟踪。

在引入 SWD 接口时,ARM 还引入了 SWD 的可选扩展,称为 Serial Wire Output, SWO。 SWO 除了 SWD 接口的调试信号外,还指定了一个专用引脚,它允许目标 CPU 通过 UART 或曼彻斯特协议在专用引脚上输出特定数据,例如 printf 输出。此引脚是单向的,因此无法在此引脚上向目标 CPU 发送数据。

ITM 和 SWO 可用于构成串行线查看器 SWV ,这提供了一种从 MCU 内部获取信息的低成本方法。

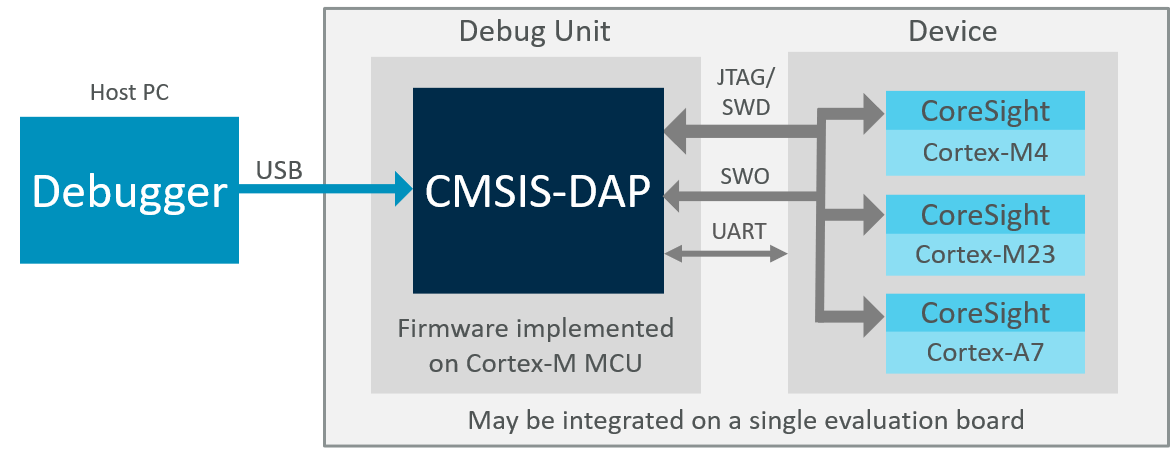

3 CMSIS-DAP

CMSIS(Common Microcontroller Software Interface Standard) 是 ARM 公司牵头为所有 Cortex-M 内核实现指定的接口标准。

而 CMSIS-DAP 则描述了如何通过 USB 连接至内核的调试端口。

CMSIS-DAP 本该是一种规范,但在发展过程中逐渐变为该规范的一种实现。后又经历重命名将这种实现的名称变为了 DAPLink 。

所以 CMSIS-DAP 是规范,而 DAPLink 是一种常见实现。但经常会混淆其使用。

- Debugger: 运行在上位机上的调试程序(如 gdb, Ds-5, MDK-5 等)。

- CoreSight: 由 ARM Cortex 处理器的提供调试与跟踪单元。

3.1 DAPLink

DAPLink V1: 使用 USB-HID 协议。

DAPLink V2: 使用 WinUSB 协议,并提供 SWO 跟踪流。

DAPLink 软件堆栈:

- CMSIS-DAP

- CMSIS-DRIVER: USART, USB

- CMSIS-RTOS(Keil RTX-5)

- USB Middleware

3.2 验证方式

必须使用“验证调试单元”中提供的脚本来验证符合 CMSIS-DAP 的调试单元。